4 BIT SAR ADC

4 bit Successive Approximation Analog to Digital Converter

Project Overview

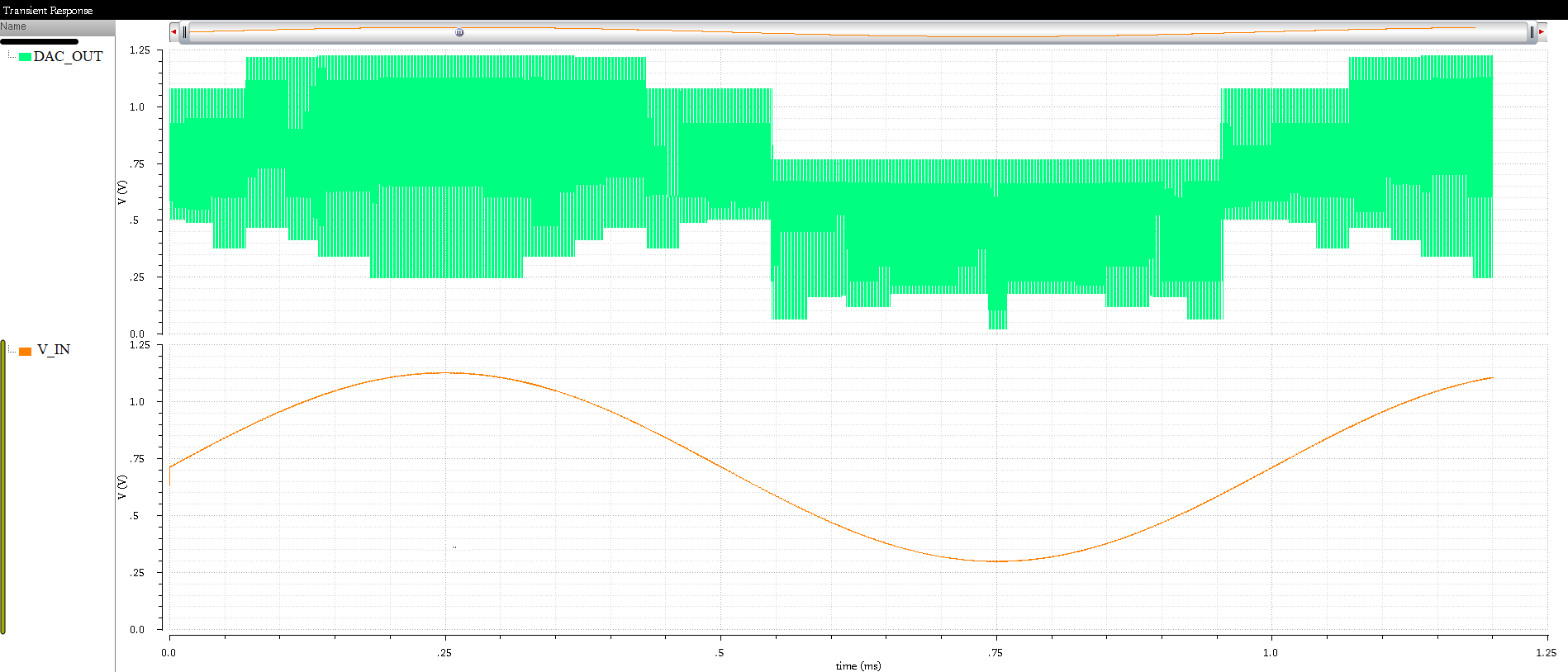

A 4 bit SAR ADC was designed as per the requirements of laboratory 3 for ELE724 (CMOS Mixed-Mode Circuits) using TSMC 130nm technology in Cadence. 4 blocks: Sample/Hold circuit, Comparator, Successive Approximation Logic and Digital to Analog converter were independently designed and integrated to form the SAR ADC. The S/H block samples the input voltage when CLK = 1 and holds the voltage level when CLK = 0. The comparator compares the S/H output with DAC output. If S/H output > DAC output, the Comparator output = 1. The Comparator output is fed into the SAR logic which then generates the corresponding analog output of the input voltage. The analog bits are then fed into the charge scaling DAC which then outputs the voltage equivalent to input voltage. The figure above shows the input voltage and the respective output voltage generated by the SAR ADC. The simulation was run for 1.2 ms (transient analysis) in Cadence Virtuoso Analog Environment and took approximately 3 hours to execute.